• CADE NCE QR C E XTR ACT ION Cadence QRC Extraction, the industry’s premier 3D full- ® chip parasitic extractor that is independent of design style or flow, is a fast and accurate RLCK extraction solution used during design implementation and validation. Its seamless integration with Cadence Encounter and Virtuoso design. • Cadence QRC Extraction models physical Process effects found in advanced process SoC Encounter System File technologies to ensure that extracted Place and Route parasitics match those on silicon.

By delivering higher-quality parasitics, it helps designers reduce overall design cycle Incremental Extraction times and significantly enhance quality of silicon in complex SoC designs. • MUlti-CoRneR extRaCtion In designs at 130nm and below, a GDSII DFII nominal corner extraction and some added margin is no longer sufficient to accurately predict parasitic effects. For example, signal integrity issues can occur Cadence Physical Verification at strong, high-temperature conditions. Thus, designers are required to perform extraction at multiple corners, and the number of corners grows as the process.

• advanCed CheMiCal- MeChaniCal poliShing (CMp) Modeling SUppoRt QRC Extraction interfaces to innovative Cadence chemical-mechanical polishing (CMP) technology for modeling full-chip Lightly doped substrate Lightly doped substrate with Heavily doped substrate thickness variation and accurately with no guard ring guard ring connected to with no guard ring ideal power supply predicting systematic variations in interconnect layer thickness (Figure 6). • © 2008 Cadence design Systems, inc. All rights reserved.

Dec 16, 2011 - My best recommendation is to review the cadence QRC manual (located in your Assura installation directory) along with your technology. Sure your layout is clean (see Tutorials 3 and 4 for reference). Now QRC can be used to extract the layout. Run QRC from QRC > Run Assura-QRC.

Cadence, assura, encounter, Spectre, virtuoso, and voltageStorm are registered trademarks and the Cadence logo and SoC encounter are trademarks of Cadence design Systems, inc. All others are properties of their respective holders.

Hello, I am having trouble running Assura RCX. I am currently using Cadence Virtuoso 6.1.3 with IBM PDK cmos10lpe (65nm). I ran Assura LVS on a simple inverter cell and it has no probem passing LVS check (I ran DRC on the same inverter with Synopsys Hercules because the IBM PDK that I am using does not provide a rule set for Assura DRC). Then I tried to run Assura RCX by selecting 'Assura ->Vb 2010 express portable free download. Run RCX' from the Virtuoso Layout Editor menu.

For some unknown reason, it causes Cadence to crash. Here is a part of the log file. O Assura RCX Run: Loading Technology Data. A leSetLSWBBox(list(9:171 159:871)) r t a leSetLSWBBox(list(9:171 159:871)) r t a leSetLSWBBox(list(9:171 159:871)) r t a leSetLSWBBox(list(9:171 159:871)) r t a leSetLSWBBox(list(9:171 159:871)) r t w *WARNING* No tech dir found for tech name NONE w *WARNING* Current technology is 'NONE', but.tpl file was not loaded for some reasons. O Template file '/n/homeserver2/user2a/mcwang/cadence/IBM_PDK/cmos10lpe/relRF/cdslib/cmos10lpe/.rcx_setup.tpl' was successfully loaded.Warning: SNA Tech Dir is not a directory, trying the default SNA Tech Dir o (dbPanic) dumping stack o dbPanic+304() I am especially puzzled by the warning '*WARNING* No tech dir found for tech name NONE' because I did specify the technology in Assura -> Setup -> RCX Setup or something like that. I definitely had specified the technology when I ran LVS earlier. I have another question regarding Cadence QRC.

Is this part of Assura instalation? I couldn't find anything that resembles QRC in the Software Download page. The IBM PDK that I am using supports QRC, but I couldn't find it in the Assura menu from the Virtuoso Layout Editor menu.

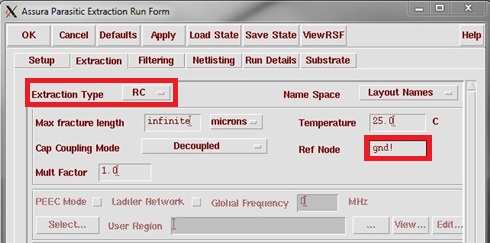

Thanks in advance. O QRC Run: Loading Technology Data. W *WARNING* Current technology is '8RF_DM_32', but.tpl file was not loaded for some reasons. O *Info* Default Substrate Tech Dir is not defined, replaced with the empty nameWarning: Substrate Tech Dir is not a directory, trying the default Substrate Tech Dir w *WARNING* No tech dir found for tech name NONE w *WARNING* Current technology is 'NONE', but.tpl file was not loaded for some reasons. (some warnings) o Load complete. W *WARNING* No tech dir found for tech name NONE w *WARNING* No technology directory found. Ansys autocad import page. To setup QRC you need to set the Technology Directory to / /Assura/QRC/, and in the Extraction tab set Reference node to /gnd!

I'm not sure but you can try setting RSF File to /QRC/ /LVSinclude.rsf. For extracting L and K you need to specifiy the User Region field and whichever metals you want to extract L and K for.